- 您现在的位置:买卖IC网 > Sheet目录1245 > SPI-324P-O4-N1 (Lattice Semiconductor Corporation)IP PHY LAYER BRIDGE SPI3-4 ORCA4

�� �

�

Quad� SPI-3� to� SPI-4� Link� Layer�

�Lattice� Semiconductor�

�Bridge� Core� User’s� Guide�

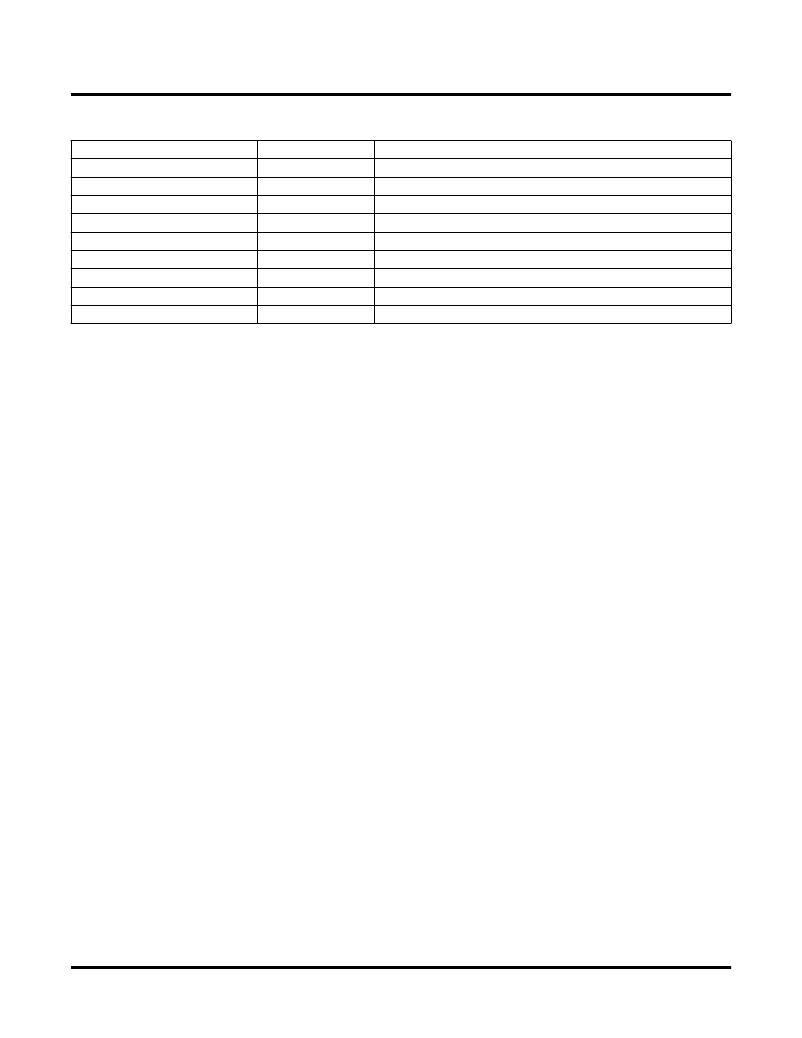

�Table� 5.� Signal� De?nitions� for� Quad� SPI-3� to� SPI-4� Link� Bridge� Solution� -� FPGA/Embedded� ASB� Interface�

�(Internal� to� ORSPI4� Device)� (Continued)�

�Signal� Name�

�TX_D[32]�

�TX_D[33]�

�TX_D[37:34]�

�TX_D[38]�

�WD_CNT_RST�

�TX_WE�

�TX_A[2:0]�

�TX_PORT[7:0]�

�FIFO_FULL�

�FPGA� Direction�

�Output�

�Output�

�Output�

�Output�

�Output�

�Output�

�Output�

�Output�

�Input�

�Description�

�SOP� Indicator� to� DPRAM� Bank� 0�

�EOP� Indicator� to� DPRAM� Bank� 0�

�Byte� Valid� Indicator� to� DPRAM� Bank� 0�

�Error� Indication� for� Write� Data�

�WCL� Word� Count� Reset� 0�

�Write� Enable� for� DPRAM� Bank� 0�

�Write� Address� for� DPRAM� Bank� 0�

�Port� ID� for� DPRAM� Bank� 0�

�FIFO� Full� Flag� from� DPRAM� Bank� 0�

�1.� The� signals� listed� here� are� required� for� a� single� SPI-3� interface.� The� signals� should� be� replicated� for� each� additional� SPI-3� Interface� instan-�

�tiation.� The� status� signals� in� both� receive� and� transmit� directions� between� the� FPGA� and� the� embedded� Application� Speci?c� Block� (ASB)�

�are� not� replicated� when� the� core� has� multiple� SPI-3� interfaces.�

�SPI-3� I/O� Timing� and� Electrical� Speci?cations�

�The� examples� in� the� following� sections� are� provided� to� aid� in� the� visualization� of� the� interface� operation.�

�Transmit� Logical� Timing�

�Figure� 3� shows� transactions� on� a� SPI-3� Transmit� interface� with� two� ports.� The� SPI-3� transmit� interface� is� controlled�

�by� the� Link� Layer� device� using� the� TENB� signal.� All� signals� must� be� updated� and� sampled� using� the� rising� edge� of�

�the� transmit� FIFO� clock,� TFCLK.� The� PHY� Layer� device� indicates� that� a� FIFO� is� not� full� by� asserting� the� appropriate�

�transmit� packet� available� signal� DTPA.� DTPA� remains� asserted� until� the� transmit� FIFO� is� almost� full.� “Almost� full”�

�implies� that� the� PHY� Layer� device� can� accept,� at� most,� a� prede?ned� number� of� writes� after� the� current� write.�

�If� DTPA� is� asserted� and� the� Link� Layer� device� is� ready� to� write� a� word,� it� should� assert� TSX,� de-assert� TENB� and�

�present� the� port� address� on� the� TDAT� bus� if� required.� Subsequent� data� transfers� with� TENB� low� are� treated� as�

�packet� data,� which� is� written� to� the� selected� FIFO.� At� any� time,� if� the� Link� Layer� device� does� not� have� data� to� write,�

�it� can� de-assert� TENB.� The� TSOP� and� TEOP� signals� must� be� appropriately� marked� at� the� start� and� end� of� packets�

�on� the� TDAT� bus.�

�When� DTPA� transitions� low� and� it� has� been� sampled,� the� Link� Layer� device� can� write� no� more� than� a� prede?ned�

�number� of� bytes� to� the� selected� FIFO.� In� this� particular� example,� the� prede?ned� value� is� two� double-words� or� eight�

�bytes.� In� the� IP� core� implementation,� if� DTPA� is� high� the� PHY� Layer� can� accept� a� complete� burst.� When� the� DTPA�

�is� deasserted� the� PHY� Layer� can� accept� the� burst� being� transferred� but� no� more.� If� the� Link� Layer� writes� more� than�

�that� prede?ned� number� of� words� and� DTPA� remains� deasserted� throughout,� the� PHY� Layer� device� should� indicate�

�an� error� condition� and� ignore� additional� writes� until� it� asserts� DTPA� again.�

�12�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SPN02SVBN-RC

CONN JUMPER SHORTING 2MM GOLD

SPN02SVEN-RC

CONN JUMPER SHORTING 2MM GOLD

SPN02SXCN-RC

CONN JUMPER SHORTING 2MM GOLD

SPT711XPFCE

CARD TELEPHONY FARM CRD 711X

SPUSB1AJT

SURGE SUPPRESOR USB 12OHM SC70-6

SR-5H-6.3A-BK

FUSE 6.3A 250VAC RADIAL SLOW

SR1K20M155X

VARISTOR 20VRMS W/RFI SUPP RAD

SRP120LF

POLYSWITCH PTC RESET 1.2A STRAP

相关代理商/技术参数

SPI-333-34AB

制造商:SANYO Semiconductor Co Ltd 功能描述:

SPI-335-34

制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Ultraminiature photoreflector (single-transistor type)

SPI-336-99-T1

制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Ultraminiature photoreflector supporting reflow soldering Single transistor type

SPI3501UH

制造商:SPI 制造商全称:SPI 功能描述:350 Watts EPS12V 1U Switching Power Supply

SPI3501UH-B204

制造商:Sparkle Power Inc 功能描述:POWER SUPPLY,SWITCHING,ENCLOSED,1U,350 WATT,ATX/EPS,PFC,(2)1

SPI350ACA8

制造商:SPI 制造商全称:SPI 功能描述:350 Watts, ATX Switching Power Supply

SPI350ACAG

制造商:SPI 制造商全称:SPI 功能描述:350 Watts ATX12V 2.3 Switching Power Supply Meet 2010 ErP

SPI350GLN

制造商:Sparkle Power Inc 功能描述:POWER SUPPLY,SWITCHING,ATX,350 WATT,ATX12V 2.2,PFC,(2)12VDC@